KSJ EtherCAT Master based on ARM CPU + FPGA

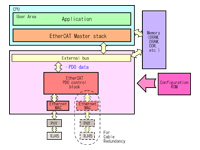

KSJ EtherCAT master stack is developed for the purpose of industrial embeded systems. This master stack works on FPGA SoCs and support ETG1500.classB standard plus DC function. Faster and low jitter cyclic PDO frames are transmitted and processed by FPGA logic which enables full CPU usage by application.

As real-time OS on ARM CPU, FreeRTOS, Xenomai, eT-Kernel, Nucleus can be supported. (Other OS can be negociatable to implement)

KSJ original LZ201 master board equipped with Xilinx Zynq SoC is helpful for evaluation. LZ201 board can achieve 20 μsec cyclic PDO communication, and about 30 nsec jitter with 3 slaves which has 32bit data for each using this Master Stack with 0% CPU usage.